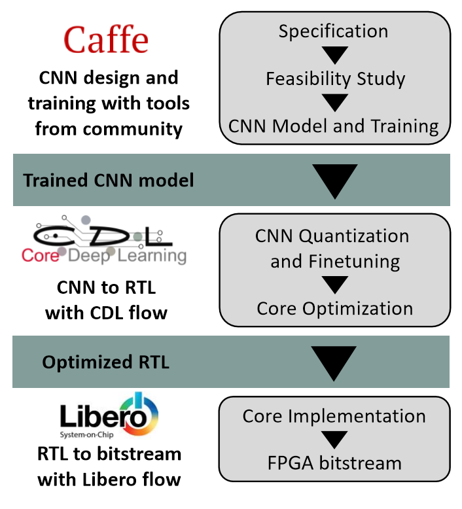

Deep Neural Network ASICs The Ultimate Step-By-Step Guide eBook : Blokdyk, Gerardus: Amazon.in: Kindle Store

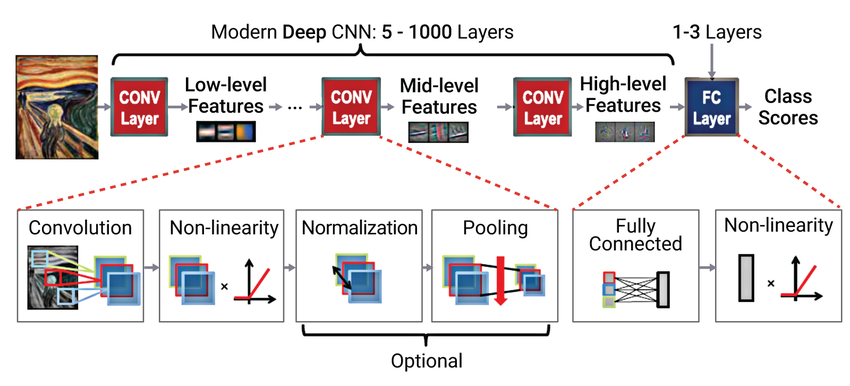

Intel Speeds AI Development, Deployment and Performance with New Class of AI Hardware from Cloud to Edge | Business Wire

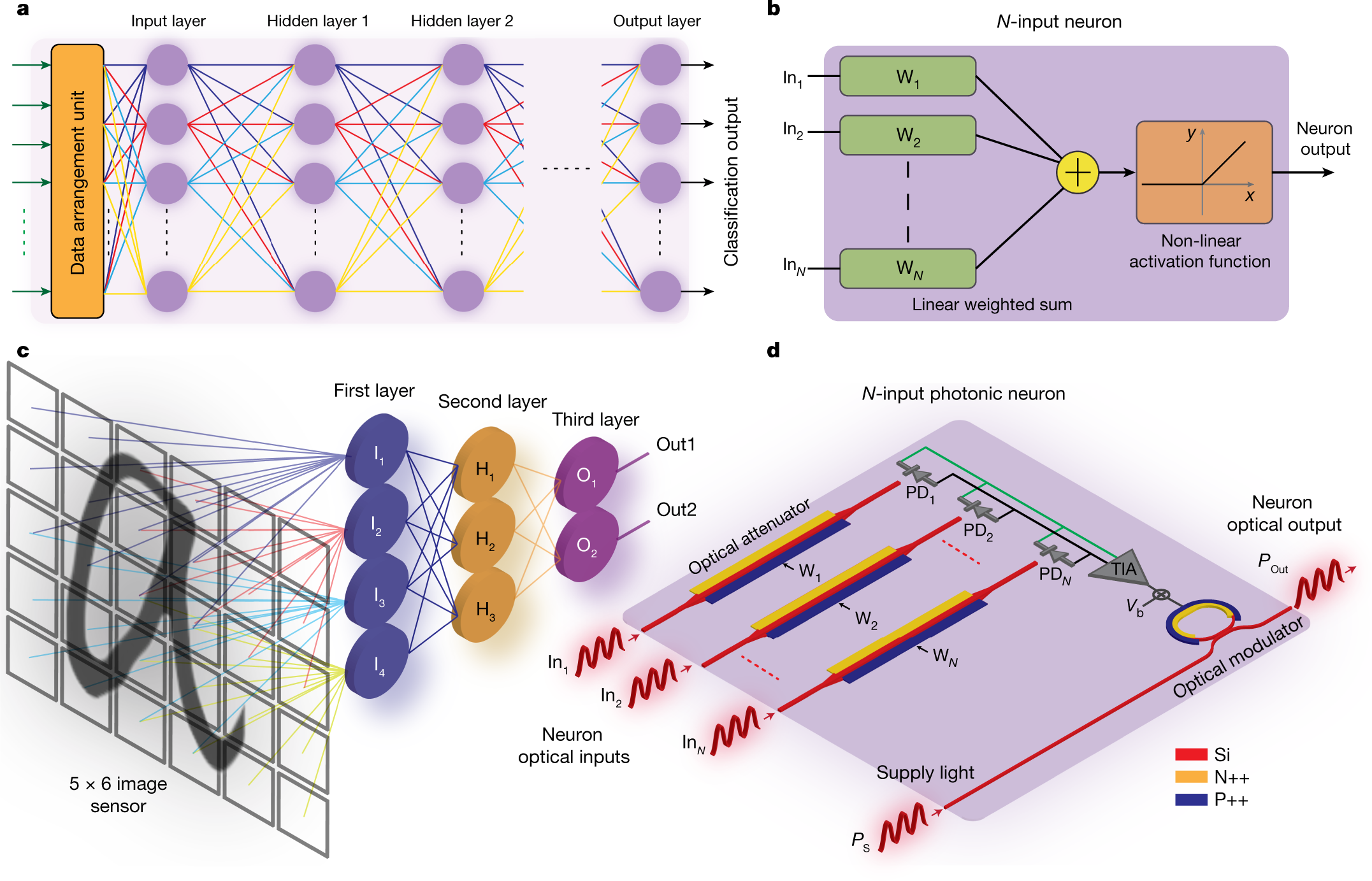

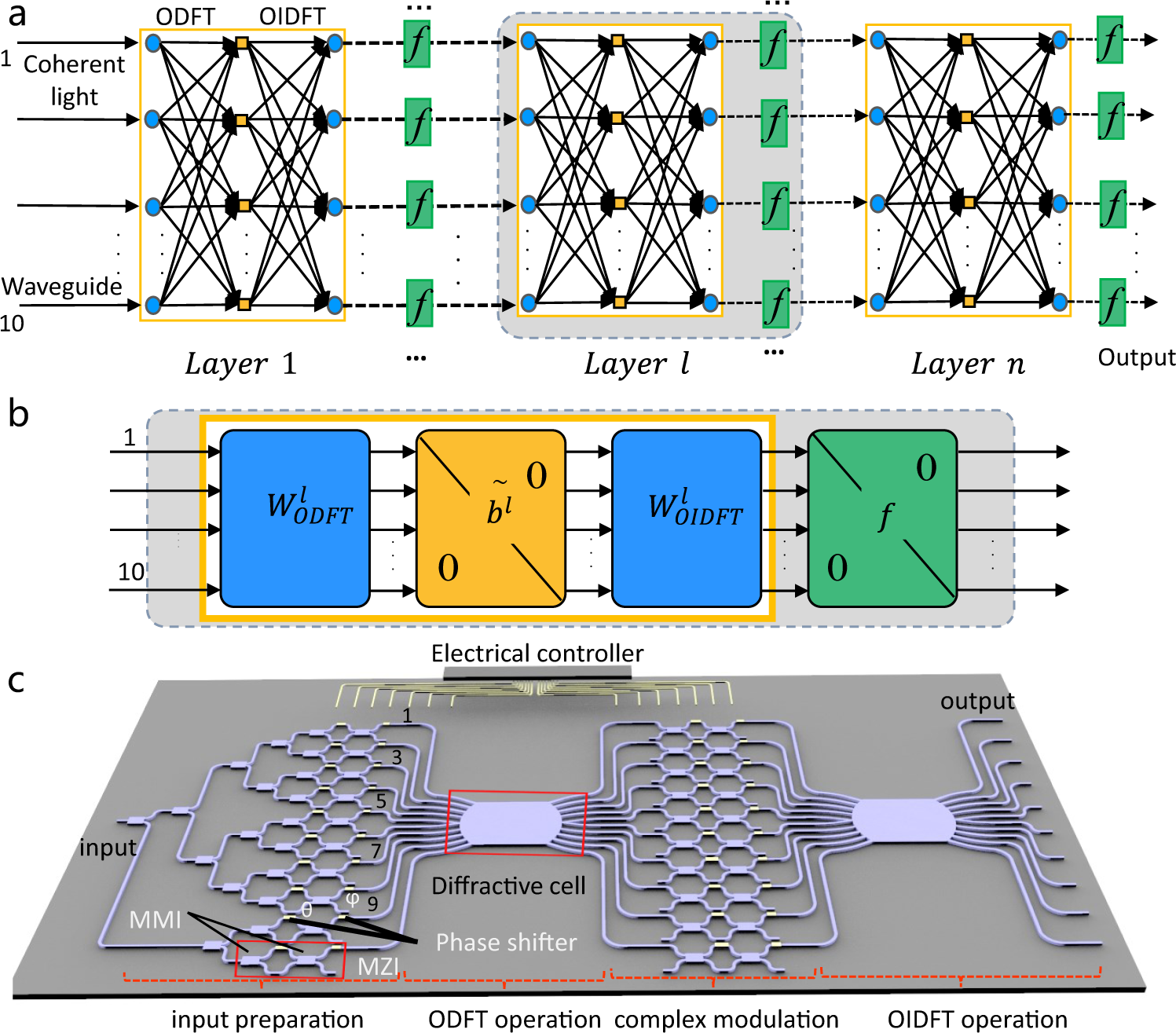

Space-efficient optical computing with an integrated chip diffractive neural network | Nature Communications

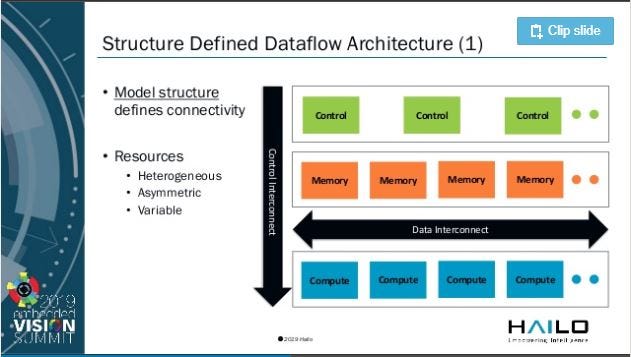

The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com